Product Summary

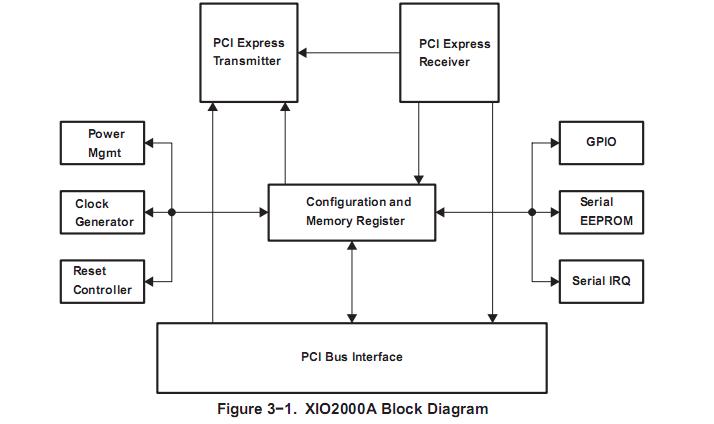

The XIO2000AZZZ is a single-function PCI Express to PCI translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. For downstream traffic, the XIO2000AZZZ simultaneously supports up to eight posted and four nonposted transactions for each enabled virtual channel(VC). For upstream traffic, up to six posted and four nonposted transactions are simultaneously supported for each VC. The XIO2000AZZZ has additional capabilities including, but not limited to, serial IRQ with MSI messages, serial EEPROM, power override, clock run, and PCI bus LOCK.

Parametrics

XIO2000AZZZ absolute maximum ratings: (1)Supply voltage range: VDD 33: -0.5 V to 3.6 V; VDD_15: -0.5 V to 1.65 V; VCCP: -0.5 V to 5.25 V; (2)Input voltage range, VI: PCI: -0.5 V to VCCP + 0.5 V; (3)VI: PCI Express (RX): -0.6 V to 0.6 V; (4)VI: PCI Express REFCLK (single-ended): -0.5 V toVDD_33 + 0.5 V; (5)VI: PCI Express REFCLK (differential): -0.5 V toVDD_15 + 0.5 V; (6)VI: Miscellaneous 3.3-V IO: -0.5 V to VDD_33 + 0.5 V; (7)Output voltage range: VO: PCI: -0.5 V to VDD_33 + 0.5 V; (8)VO: PCI Express (TX): -0.5 V to VDD_15 + 0.5V; (9)VO: Miscellaneous 3.3-V IO: -0.5 V to VDD_33 + 0.5 V; (10)Input clamp current, (VI < 0 or VI > VDD): ±20 mA; (11)Output clamp current, (VO < 0 or VO > VDD): ±20 mA; (12)Human body model (HBM) ESD performance: 1500 V; (13)Charged device model (CDM) ESD performance: 500 V; (14)Storage temperature range, Tstg: -65℃ to 150℃.

Features

XIO2000AZZZ features: (1)Full x1 PCI Express Throughput; (2)Fully Compliant with PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0; (3)Fully Compliant with PCI Express Base Specification, Revision 1.0a; (4)Fully Compliant with PCI Local Bus Specification, Revision 2.3; (5)Extended Virtual Channel (VC) Support Includes a Second VC for Quality-of-Service and Isochronous Applications; (6)PCI Express Advanced Error Reporting Capability Including ECRC Support; (7)Support for D1, D2, D3hot, and D3cold; (8)Active State Link Power Management Saves Power When Packet Activity on the PCI Express Link is Idle, Using Both L0s and L1 States; (9)Wake Event and Beacon Support; (10)Error Forwarding Including PCI Express Data Poisoning and PCI Bus Parity Errors; (11)Utilizes 100-MHz Differential PCI Express Common Reference Clock or 125-MHz Single-Ended, Reference Clock.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XIO2000AZZZ |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express-PCI Bus Translation Bridge |

Data Sheet |

Negotiable |

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

XIO2000A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AEVM |

Texas Instruments |

Interface Modules XIO2000A Eval Mod |

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AGZZ |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express-PCI Bus Translation Bridge |

Data Sheet |

Negotiable |

|

||||||||||||

|

XIO2000AIZHH |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express Bridge Industrial |

Data Sheet |

|

|

||||||||||||

|

XIO2000AIZZZ |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Express Bridge Indus ZZZ option |

Data Sheet |

|

|

||||||||||||

|

XIO2000AZHH |

Texas Instruments |

Peripheral Drivers & Components (PCIs) PCI Exp-PCI Bus Trans Bridge |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))